近十几年来,霍尔元件在已肉眼看得到的速度发展,霍尔芯片的一致性、抗静电等级、耐压值、耐温值都在不断的进度,让我们联想到了著名的摩尔定律。

5月14日,据媒体报道,刘鹤主持召开国家科技体制改革和创新体系建设领导小组第十八次会议,讨论了后面向摩尔时代的集成电路潜在颠覆性技术。

摩尔定律,这一条在集成电路行业被奉为圭臬的著名定律,起源于英特尔创始人——戈登摩尔。1965年,戈登摩尔准备一个关于计算机存储器发展趋势的报告,在他开始绘制数据时,发现了一个惊人的趋势。每个新的芯片大体上包含其前任两倍的容量,每个芯片产生的时间都是在前一个芯片产生后的18~24个月内。

此后摩尔定律略微修改,变成大家所熟知的集成电路行业最知名的定律:每隔18个月,同样面积内晶体管数量翻倍,但是价格不变。根据摩尔定律我们可以得到以下两条结论:

1、每隔18个月,单位面积内晶体数量翻倍,同时这也意味着性能也翻倍了。

2、价格不变,因此同样价格买到晶体管数量翻倍了,这等同于单个晶体管成本降低了一半。

虽然摩尔定律并不是一条自然规律,但是摩尔定律一直影响着集成电路行业技术的发展节奏。换言之当行业头部公司,在不断追求摩尔定律之时,如果竞争对手达不到,那就会竞争中就处于脱节的状态,极容易被淘汰。

摩尔定律的核心就是晶体管数量成倍增加,在同一面积内集成更多的晶体管,性能也大幅提升,同时价格不变,晶体管成本也在不断下降。

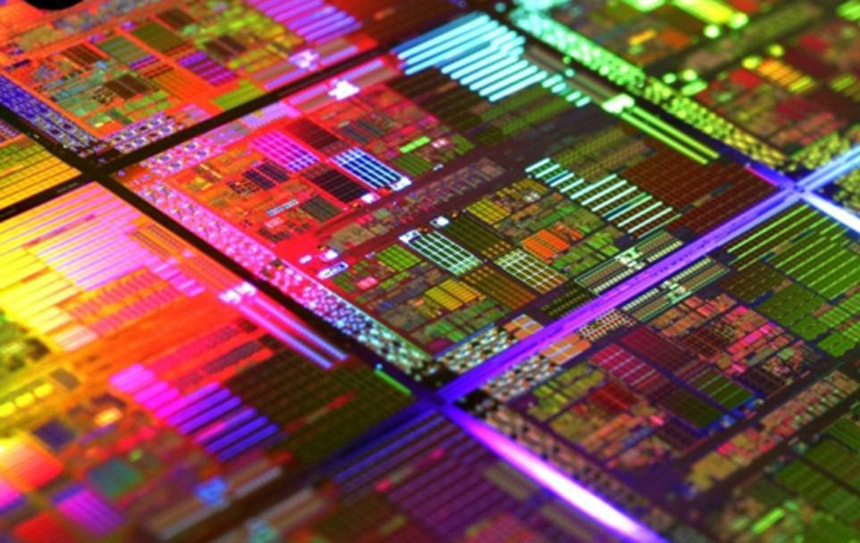

于是芯片制造技术不断前进,力图把晶体管的尺寸不断缩小。于是集成电路特征尺寸从最开始的几微米不断下降。0.5u、0.35u、0.25u、0.18u、0.13u、90nm、65nm、45nm、28nm、14nm,直到现在的7nm、5nm,前后发展了几十年时间。

但是到最近几年,摩尔定律渐渐有些力不从心了。是什么原因让摩尔定律放缓了?其实在摩尔定律的两条结论中还隐藏有第三条。

晶体管数量翻倍的同时,功耗大幅提升,发热量也翻倍了。晶体管数量翻倍带来的巨****热量,导致芯片内部变成一个大火炉,这个问题一直制约着晶体管数量的翻倍,可以说业内一直寻找各种各样的办法与发热量做斗争。

因此摩尔定律想要维持下去的,必须面临以下两个问题。

物理极限的技术问题:

目前实际商业化的技术是5nm,未来可能还有3nm、2nm,甚至1nm,但是实际上技术升级的空间已经变的很小了,因为不断的微缩的晶体管已经快要逼近物理极限,特别是晶体管的特征尺寸——栅极宽度已经小到真的很难控制了。

在28nm以下的工艺,平面晶体管已经走到极限,于是已经用业内用FinFET晶体管结构替代了原本的平面结构,继续保持单位面积内的晶体管密度翻倍。但是其实晶体管的特征尺寸——栅极宽度并没有变化太多,但是业内依然以14nm来命名(台积电是16nm),其实此处的14nm,准确的说应该是等效工艺,并非栅极宽度真的是14nm。

虽然目前用FinFET,甚至未来的GAA、MBCFET等立体晶体管结构的来给摩尔定律续命,但是迟早有一天会达到硅材料的极限。不可能永无止境的去缩微晶体管尺寸,并增加晶体管密度。

所有人都知道迟早有一天,集成电路微缩工艺会卡在某个物理极限节点而无法继续前进。

成本高昂的商业问题:

摩尔定律的第二条,单个晶体管成本不断降低,换言之付出同样的价格,可以买到性能更强的芯片,但是随着工艺逼近极限,在巨大的研发费用和建厂成本下,芯片生产成本不降反升。

其中巨额的研发投入,一大半就是与发热量做斗争。

发热量来自两个部分,一是晶体管本身工作时带来的热量,第二是金属互联层带来的热量。

所以业内一方面在寻找各种能替代硅晶体管的材料。另外一方面就是寻找现有金属互联层的替代材料,包括阻挡层材料、接触点材料等。这些都算到工艺研发成本中,目前已经是天文数字。

而巨大的建厂成本带来的问题也不容小觑,以台积电3nm工厂为例,建厂成本为200亿美金,折合人民币超过1300亿。

理所当然,3nm建厂成本和研发成本都要分摊到生产的每一颗芯片上,综合巨大和建厂的巨额成本,这导致了未来单个晶体管的成本不降反升的情况。

就这个角度而言,摩尔定律其实已经失效了。

所以摩尔定律迟早会有一天停下它的脚步,而后摩尔时代应该如何继续发展呢?

如果您想了解更多华芯霍尔元件产品信息,欢迎访问我们的官网https://www.wxhxkj.com/或者https://www.chhxs.cn/,无锡华芯科技竭诚为您服务!

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。